#### **FEATURES**

- 100MHz conversion rate

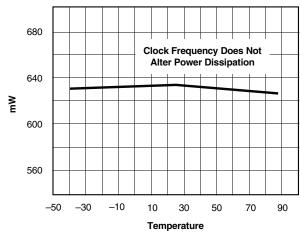

- Low power, 650mW, typical

- Low glitch energy, 3.0pV-s

- Excellent dynamic specifications

- TTL/CMOS compatible inputs

- 20ns settling time

- Packaged in a hermetic ceramic LCC package (0.450 X 0.450 inches)

- Standard versions come with solder dipped leads

- Low cost

- Models available in commercial (0 to + 70°C), industrial (-40 to +100°C), or military (-55 to +125°C) operating temperature ranges

- Full 883 and LM/QL versions available

- If needed a ROHS version is available

#### PRODUCT OVERVIEW

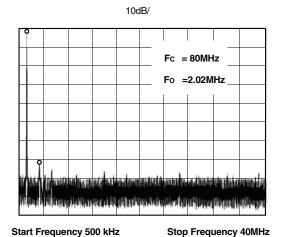

The DAC-12100 is a 12-bit, ultra high speed, current output digital-to-analog converter. This TTL/CMOS compatible device converts at a rate of 100MHz and features a 3.0 pV-s glitch energy and excellent frequency domain specifications. The DAC-12100 develops complementary current outputs of 0 to  $-20.48 \mathrm{mA}$  and can directly drive 50 0hm loads. The excellent dynamic specifications (to Nyquist at f0UT=2.02MHz) include an SFDR of  $-85 \mathrm{dB}$ . Static performance includes maximum over temperature specifications of +/- 1.75LSB and +/-1LSB for integral and differential nonlinearity, respectively.

The DAC-12100 achieves low power and high speed performance from an advanced BiCMOS process.

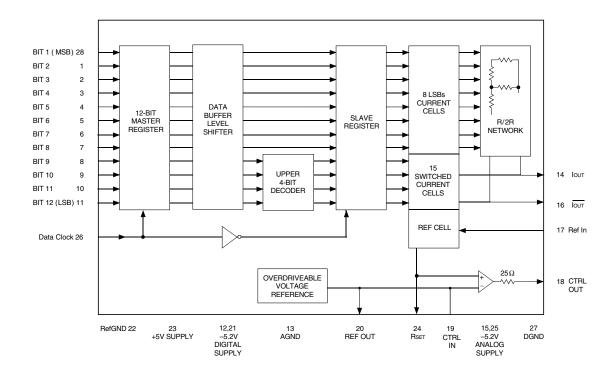

The architecture employs an R/2R resistor network and a segmented switching current cell arrangement to reduce glitch. Laser trimming assures that 12-bit linearity is achieved and maintained over the transfer curve. It also incorporates a 12-bit input data register and bandgap voltage reference with a buffer amplifier.

The DAC-12100 runs on +5V and -5.2V supplies and dissipates a maximum of 800mW. It is available in a 28-pin CLCC solder dipped leads package with an operating temperature range of 0 to 70°C and -55 to +125°C. If needed a RoHS version is available upon request.

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1. Functional Block Diagram

DATEL, Inc. 11 Cabot Boulevard, Mansfield, MA 02048-1151 USA • Tel: (508) 339-3000 • www.datel.com • e-mail: help@datel.com

# 12-Bit, 100MHz, Low-Power D/A Converters

| ABSOLUTE MAXIMUM RATINGS                 |                                |       |

|------------------------------------------|--------------------------------|-------|

| PARAMETERS                               | LIMITS                         | UNITS |

| +5V Digital Supply                       | +5.5                           | Volts |

| -5.2V Digital Supply                     | -5.5                           | Volts |

| -5.2V Analog Supply                      | -5.5                           | Volts |

| Digital Input Voltages                   | -0.5 to +5V Supply level       | Volts |

| Internal Reference Output Current        | ±2.5                           | mA    |

| Voltage from CTRL IN to -5.2V (A) Supply | 2.5 to 0                       | Volts |

| CTRL OUT Output Current                  | ±2.5                           | mA    |

| Reference Input Voltage Range            | -5.2V (A) Supply Level to -3.7 | Volts |

| Analog Output Current, IOUT              | 30                             | mA    |

| Lead Temperature (10 seconds)            | 300                            | °C    |

| PHYSICAL/ENVIRONMENTAL      |             |      |      |        |

|-----------------------------|-------------|------|------|--------|

| PARAMETERS                  | MIN.        | TYP. | MAX. | UNITS  |

| Operating Temperature Range |             |      |      |        |

| DAC-12100LC                 | 0           | _    | +70  | °C     |

| DAC-12100LE                 | -40         | _    | +100 | °C     |

| DAC-12100LM                 | -55         | _    | +125 | °C     |

| Storage Temperature Range   | -65         | _    | +150 | °C     |

| Thermal Resistance, θja     |             | 24   |      | (°C/W) |

| Junction Temperature        | _           | _    | +150 | °C     |

| Package Type                | 28 Pin CLCC |      |      |        |

## **FUNCTIONAL SPECIFICATIONS**

(TA = See specification table, -5.2V (A) Supply = -5.2V (D) Supply = -4.94 to -5.46V, +5V Supply = 4.75 to 5.25V, VREF = Internal, RL = 50 Ohms and fs = 100MHz unless otherwise specified.)

|                                       |       | 0 TO +70°C  |      |       | –55 TO +125°C |                  |            |

|---------------------------------------|-------|-------------|------|-------|---------------|------------------|------------|

| DIGITAL INPUTS                        | MIN.  | TYP.        | MAX. | MIN.  | TYP.          | MAX.             | UNITS      |

| Resolution                            | 12    | _           |      | 12    | _             | _                | Bits       |

| Logic Levels                          |       |             |      |       |               |                  |            |

| Logic "1"                             | +2.0  | _           | _    | +2.0  | _             | _                | Volts      |

| Logic "0"                             | _     | _           | +0.8 | _     | _             | +0.8             | Volts      |

| Logic Loading "1"                     | _     |             | 400  | _     | _             | 400              | μA         |

| Logic Loading "0"                     | _     | _           | 700  | _     | _             | 700              | μ <u>A</u> |

| Digital Input Capacitance, CIN        | _     | 3.0         | 15   | _     | 3.0           | 15               | pF         |

| TIMING CHARACTERISTICS                |       |             |      |       |               |                  |            |

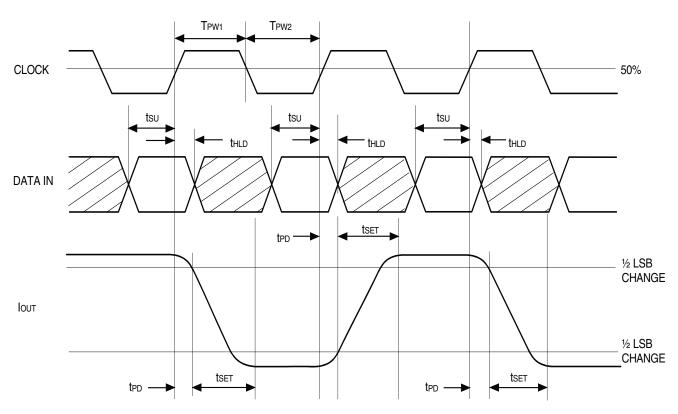

| Data setup time, tsu                  | 3     | 2           | _    | 3     | 2             | _                | ns         |

| Data Hold Time, thld                  | 0.5   | 0.25        | _    | 0.5   | 0.25          | _                | ns         |

| Propagation Delay Time, tpd           | _     | 4.5         | 7    | _     | 4.5           | 7                | ns         |

| CLOCK Pulse Width, Tpw1, Tpw2         | 3     | _           | _    | 3     | _             | _                | ns         |

| STATIC PERFORMANCE                    |       |             |      |       |               |                  |            |

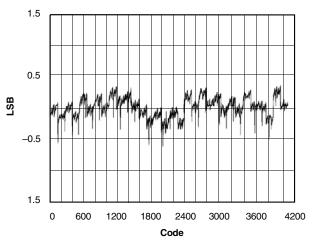

| Integral Nonlinearity ①               | _     | ±0.75       | ±1.0 | _     | ±1.0          | ±1.75            | LSB        |

| Differential Nonlinearity             | _     | ±0.5        | ±.75 | _     | 0.5           | ±1               | LSB        |

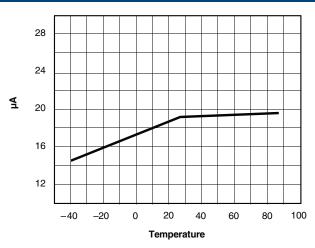

| Offset Error                          | _     | 20          | 75   | _     | 20            | 75               | μΑ         |

| Gain Error ②                          | _     | ±1          | ±10  | _     | ±1            | ±10              | %          |

| DYNAMIC PERFORMANCE                   |       |             |      |       |               |                  |            |

| Conversion Rate ③                     | 100   | _           | _    | 100   | _             | _                | MHz        |

| Output Voltage Settling Time, tSET    |       |             |      |       |               |                  |            |

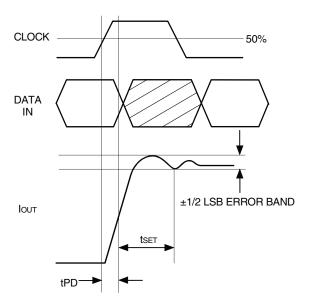

| Full Scale Step to ±1LSB              | _     | 11          | 13   | _     | 12            | 15               | ns         |

| Full Scale Step to ±0.5LSB            | _     | 20          | 22   | _     | 20            | 22               | ns         |

| Glitch Area                           |       | _           |      |       | _             |                  |            |

| Singlet (Peak)                        | _     | 2           | 10   | _     | 2             | 10               | pV-s       |

| Doublet (Net)                         | _     | 3           | _    | _     | 3             | _                | pV-s       |

| Output Slew Rate                      | 900   | 1000        | _    | 900   | 1000          | _                | V/µs       |

| Output Rise Time                      | 625   | 675         | _    | 625   | 675           | _                | ps         |

| Output Fall Time<br>Differential Gain | 425   | 470<br>0.15 | _    | 425   | 470<br>0.15   | _                | ps<br>%    |

| Differential Phase                    | _     | 0.15        | _    | _     | 0.15          |                  |            |

| Spurious Free Dynamic Range, SFDR     | _     | 0.07        | _    | _     | 0.07          | _                | Deg        |

| fCLK=10MSPS, fOUT=1.23MHz             |       |             |      |       | 82            | 77               | dB         |

| fCLK=20MSPS, fOUT=5.055MHz            | _     | _           | _    | _     | 77            | 7 <i>1</i><br>74 | dB         |

| fCLK=40MSPS, fOUT=16 MHz              |       |             |      |       | 77<br>75      | 74<br>71         | dB         |

| fCLK=40MSFS, 100T=10 MHz              |       |             |      |       | 80            | 71<br>76         | dB         |

| fCLK=80MSPS, fOUT= 10.1MHz            | _     | _           | _    | _     | 78            | 76<br>75         | dB         |

| fCLK=100MSPS, f0UT=10.1MHz            | _     | _           | _    | _     | 78<br>79      | 75<br>75         | dB         |

| Throughput rate                       | 100   | _           | _    | 100   | <del></del>   | <del></del>      | MSPS       |

| ANALOG OUTPUT                         | 100   |             |      | 100   |               |                  | MOI O      |

| Full Scale Output Current             | _     | -20.48      | _    | _     | -20.48        | _                | mA         |

| Output Voltage Compliance ④           | -1.25 |             | 0    | -1.25 |               | 0                | Volts      |

| Jaspas Foliago Compilation &          | 1.20  |             | · ·  | 1.20  |               | •                | 1010       |

## 12-Bit, 100MHz, Low-Power D/A Converters

|                                                                                           |       | 0 TO +70°C |       | -     | 55 TO +125°C |       |               |

|-------------------------------------------------------------------------------------------|-------|------------|-------|-------|--------------|-------|---------------|

| INTERNAL REFERENCE/AMPLIFIER                                                              | MIN.  | TYP.       | MAX.  | MIN.  | TYP.         | MAX.  | UNITS         |

| Reference Voltage, VREF                                                                   | -1.27 | -1.23      | -1.17 | -1.27 | -1.23        | -1.17 | Volts         |

| Reference Voltage Drift                                                                   | _     | 50         | 100   | _     | 175          | 100   | μV/°C         |

| Reference Current Sink/Source Capability<br>Reference Load Regulation                     | -125  |            | +50   | -125  | _            | +50   | μА            |

| $(IREF = 0 \text{ to } -125\mu\text{A})$                                                  | _     | 50         | _     | _     | 50           | _     | μV            |

| Reference Input (CTRL IN) Impedance<br>Reference Input (CTRL IN)<br>Multiplying Bandwidth | _     | 12         | _     | 10    | 12           | _     | kOhms         |

| (100mV sine wave, to -3dB loss at IOUT)                                                   | 50    | 200        | _     | 50    | 200          | _     | MHz           |

| Input Impedance at REF OUT Amplifier Large Signal Bandwidth                               | 3     | 1.4        | _     | 3     | 1.4          | _     | kOhms         |

| (4V p-p sine wave input, to slew rate limit)<br>Amplifier Small Signal Bandwidth          | 1     | 3          | _     | 1     | 3            | _     | MHz           |

| (1V p-p sine wave input, to –3dB loss)                                                    | 4     | 10         | _     | 4     | 10           | _     | MHz           |

| POWER REQUIREMENTS                                                                        |       |            |       |       |              |       |               |

| Power Supply Ranges                                                                       |       |            |       |       |              |       |               |

| +5V Supply                                                                                | +4.75 | _          | +5.25 | +4.75 | _            | +5.25 | Volts         |

| -5.2V Supplies<br>Power Supply Currents                                                   | -4.94 | _          | -5.46 | -4.94 | _            | -5.46 | Volts         |

| +5V Supply                                                                                | _     | 13         | 20    | _     | 13           | 20    | mA            |

| -5.2V Digital Supply                                                                      | _     | 70         | 85    | _     | 70           | 95    | mA            |

| -5.2V Analog Supply                                                                       | _     | 42         | 50    | _     | 42           | 50    | mA            |

| Power Dissipation                                                                         | _     | 650        | 800   | _     | 650          | 800   | mW            |

| Power Supply Rejection (±5% variation)                                                    | _     | 5          | 10    | _     | 5            | 10    | μ <b>A</b> /V |

#### Footnotes:

- ① Best fit straight line.

- @ Gain Error measured as the error in the ratio between the full scale output current and the current through Rset (1.28mA typ.). Ideally the ratio should be 16.

- ③ Clock frequency range is from DC to the guaranteed minimum conversion rate.

- Dynamic Range must be limited to a 1V swing within the compliance range.

## **TECHNICAL NOTES**

#### **Clock Termination**

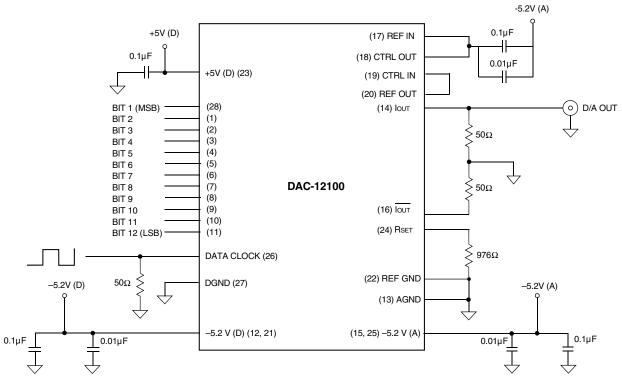

The internal 12-bit register is updated on the rising edge of the Data Clock (pin 26). To minimize reflections and noise at high clock speeds proper termination techniques should be used. In the PCB layout the clock runs should be kept as short as possible and have minimal loading. The PCB should employ a controlled characteristic line impedance ( $Z_0$ ) of 50 Ohms. A shunt termination resistor, equal to  $Z_0$ , should be placed as close to the CLOCK pin as possible, see Figure 2. The rise, fall and propagation delay times will be effected by the shunt termination resistor.

#### **Digital Inputs**

The DAC-12100 is TTL/CMOS compatible. Data is latched by a Master register.

#### **Outputs**

The outputs lout (pin 14) and lout (pin 16) are complementary current out-

puts. Current is steered to either lout or lout in proportion to the input code. The sum of the two currents is always equal to the full scale current minus one LSB. See Table 1. The output can be converted to a voltage through a load resistor, typically 50 Ohms. Both current outputs should have the same load resistance value. See Figure 2. The output voltage generated is:

Vout = Iout (Rout II 227 Ohms)

where 227 Ohms is the nominal DAC output resistance.

**Table 1. Input Coding Table**

| INPUT CODE |         |           |           |  |  |

|------------|---------|-----------|-----------|--|--|

| MSB        | LSB     | lout (mA) | lout (mA) |  |  |

| 1111 11    | 11 1111 | -20.48    | 0         |  |  |

| 1000 00    | 00 0000 | -10.24    | -10.24    |  |  |

| 0000 00    | 00 0000 | 0         | -20.48    |  |  |

#### **POWER SUPPLIES**

In order to reduce power supply noise separate -5.2V analog and digital power supplies should be used. The power supply lines should be bypassed with  $0.1\mu F$  and  $0.01\mu F$  ceramic capacitors placed as close to the -5.2V analog pins (15, 25) and digital pins (12, 21) as possible. The analog and digital power supply ground returns should be connected at one point as close to the power source as possible. The +5V supply pin (23) should be bypassed with a  $0.1\mu F$  ceramic capacitor connected as close to the pin as possible. See Figure 2.

#### REFERENCE

The internal reference is a -1.23V, typical, bandgap voltage reference. The internal reference is connected to Reference OUT (REF OUT, pin 20) and the internal control Amplifier (CTRL IN, pin 19). The control Amplifier OUT (CTRL OUT, pin 18) should be connected to Reference IN (REF IN, pin17) and to -5.2V (pin 15) Analog Supply through a  $0.1\mu F$  and a  $0.01\mu F$  ceramic capacitor (as shown in figure 2) in order to improve the settling time This reduces switching noise and improves output settling time. The Full Scale Output Current,  $\overline{lout}$  (pin 14) and  $\overline{lout}$  (pin 16), is controlled by the REF OUT (pin 20) voltage and the RSET (pin 24) resistor through the following equation:

Full Scale lout = (REF OUT Voltage/Rset Resistance) x 16

The internal reference (REF OUT) may be overdriven with a more precise external reference, capable of delivering up to 2mA, to provide better over temperature performance.

**Figure 2. Typical Connection Diagram**

Figure 3a. Timing Diagram

Figure 3b. Full Scale Settling Time Diagram

Figure 4a. Typical Power Dissipation Over Temperature

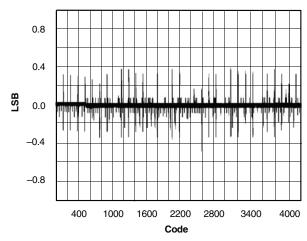

Figure 4c. Typical INL

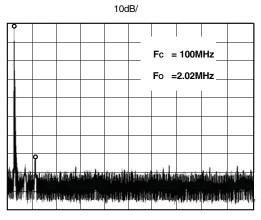

Figure 4e. Spurious Free Dynamic Range = 70.5dB

Figure 4b. Offset Current Over temperature

Figure 4d. Typical DNL

Start Frequency 500 kHz

Stop Frequency 50MHz

Figure 4f. Spurious Free Dynamic range = 70dB

### INPUT/OUTPUT CONNECTIONS

| PIN | FUNCTION                                                                 | PIN | FUNCTION                                                                                          |

|-----|--------------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------|

| 1   | D2, Digital input bit 2                                                  | 28  | D1 (MSB), Digital input bit 1                                                                     |

| 2   | D3, Digital input bit 3                                                  | 27  | DGND, Digital Ground                                                                              |

| 3   | D4, Digital input bit 4                                                  | 26  | Data Clock Pin (Rising Edge)                                                                      |

| 4   | D5, Digital input bit 5                                                  | 25  | ANALOG VEE, Nomimally -5.2V                                                                       |

| 5   | D6, Digital input bit 6                                                  | 24  | RSET, where RSET=(VREF OUT/ FS lout) x 16                                                         |

| 6   | D7, Digital input bit 7                                                  | 23  | DIGITAL Vcc, Nomimally +5V                                                                        |

| 7   | D8, Digital input bit 8                                                  | 22  | REF GND, Connected closely to pin 13 & Rset ground side                                           |

| 8   | D9, Digital input bit 9                                                  | 21  | DIGITAL VEE, Nomimally -5.2                                                                       |

| 9   | D10, Digital input bit 10                                                | 20  | REF OUT, -1.23V typ. connected<br>to CTRL AMP IN (Pin 19), Can<br>be connected to an External Ref |

| 10  | D11, Digital input bit 11                                                | 19  | CONTROL AMP IN, Connected<br>to REF OUT (Pin 20), Can be<br>connected to an External Ref          |

| 11  | D12, (LSB) Digital input bit 12                                          | 18  | CONTROL AMP OUT, Usually connected to REF IN (Pin 17)                                             |

| 12  | DIGITAL VEE, Nomimally -5.2V                                             | 17  | REF IN, Usually connected to CTRL AMP OUT (Pin 18)                                                |

| 13  | ANALOG GND, Connected closely to pin 22 & RSET ground side               | 16  | loυτ, Complementary analog<br>output current, Zero scale output<br>when all "1"                   |

| 14  | lout, Analog output current,<br>Full scale output when inputs<br>all "1" | 15  | ANALOG VEE, Analog VEE,<br>Nominally -5.2V                                                        |

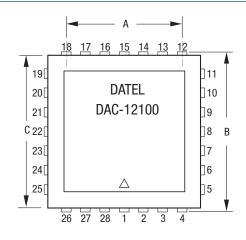

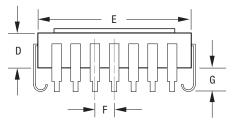

## **MECHANICAL DIMENSIONS (inches (mm))**

| SYMBOL | INCHES |

|--------|--------|

| Α      | 0.300  |

| В      | 0.466  |

| С      | 0.450  |

| D      | 0.090  |

| E      | 0.420  |

| F      | 0.050  |

| G      | 0.055  |

## **ORDERING INFORMATION**

| MODEL           | OPERATING TEMPERATURE RANGE | PACKAGE     | ROHS |

|-----------------|-----------------------------|-------------|------|

| DAC-12100LC     | 0 to 70°C                   | 28-PIN CLCC | No   |

| DAC-12100LC-C   | 0 to 70°C                   | 28-PIN CLCC | Yes  |

| DAC-12100LE     | −40 to 100°C                | 28-PIN CLCC | No   |

| DAC-12100LE-C   | −40 to 100°C                | 28-PIN CLCC | Yes  |

| DAC-12100LM     | −55 to 125°C                | 28-PIN CLCC | No   |

| DAC-12100LM-C   | −55 to 125°C                | 28-PIN CLCC | Yes  |

| DAC-12100/883   | −55 to 125°C                | 28-PIN CLCC | No   |

| DAC-12100/883-C | −55 to 125°C                | 28-PIN CLCC | Yes  |

Solder dipping is available on Non-RoHs compliant parts.

DATEL is a registered trademark of DATEL, Inc. 11 Cabot Boulevard, Mansfield, MA 02048-1151 USA ITAR and ISO 9001/14001 REGISTERED

DATEL, Inc. makes no representation that the use of its products in the circuits described herein, or the use of other technical information contained herein, will not infringe upon existing or future patent rights. The descriptions contained herein do not imply the granting of licenses to make, use, or sell equipment constructed in accordance therewith. Specifications are subject to change without notice.

© 2015 DATEL, Inc.